# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(45) 공고일자 2019년04월03일 (11) 등록번호 10-1935348

(51) 국제특허분류(Int. Cl.) *H01L 45/00* (2006.01)

(52) CPC특허분류

**H01L 45/06** (2013.01) **H01L 45/1253** (2013.01)

(21) 출원번호10-2017-0061660(22) 출원일자2017년05월18일심사청구일자2017년05월18일(65) 공개번호10-2018-0126801

(43) 공개일자 **2018년11월28일**

(56) 선행기술조사문헌 JP2012209569 A\* KR1020120083310 A\* KR1020140030606 A\* KR1020130117695 A\*

\*는 심사관에 의하여 인용된 문헌

(24) 등록일자 (73) 특허권자

## 세종대학교산학협력단

서울특별시 광진구 능동로 209 (군자동, 세종대학 교)

2018년12월28일

(72) 발명자

#### 이원준

서울특별시 마포구 독막로42길 2, 108동 704호 ( 염리동, 마포자이)

## 박재민

울산광역시 남구 대학로47번길 5, 401호 (무거동)

#### 김예원

경상북도 상주시 상산로 147, 107동 1009호 (신봉 동, 동아아파트)

(74) 대리인

특허법인엠에이피에스

전체 청구항 수 : 총 19 항

심사관 : 나영준

# (54) 발명의 명칭 다충 상변화 물질막 및 이의 제조 방법, 이를 포함하는 상변화 메모리 소자

## (57) 요 약

다층 상변화 물질막 및 상기 다층 상변화 물질막의 제조 방법, 및 상기 다층 상변화 물질막을 포함하는 상변화 메모리 소자에 관한 것이다.

# 대 표 도 - 도2

# (52) CPC특허분류

*H01L 45/14* (2013.01) *H01L 45/1608* (2013.01)

이 발명을 지원한 국가연구개발사업

과제고유번호 1415131708 부처명 미래창조과학부

연구관리전문기관 한국산업기술평가관리원 연구사업명 전자정보디바이스산업원천기술개발

연구과제명 신공정 및 metrology 연구를 통한 차세대 PCRAM 기술 개발

기 여 율 1/1

주관기관연세대학교산학협력단연구기간2013.06.01 ~ 2018.05.31

# 명 세 서

### 청구범위

#### 청구항 1

복수 층의 상변화 물질막; 및

상기 상변화 물질막의 각 층 사이에 형성된 분리막

을 포함하는, 다층 상변화 물질막으로서,

상기 분리막은 상기 상변화 물질막의 층들 사이의 원소 이동을 방지하는 것이고, 상기 분리막은 비옥사이드계 물질을 포함하는 것이고,

상기 상변화 물질막의 각 층은 A-B-C 상변화 물질을 포함하는 것이며,

상기 상변화 물질막의 각 층은,

A-B 막을 형성하는 단계; 및

상기 형성된 A-B막을 칼코겐 원소 C-함유 전구체를 포함하는 기체 분위기 하에서 어닐링하는 것에 의하여 상기 A-B 막을 칼코게나이드화함으로써 칼코겐-함유 A-B-C 막을 형성하는 단계를 통해 제조되는 것이고,

여기서, A는 Ge, Sn, Si, In, Al, Ag, 및 Ga를 포함하는 군으로부터 적어도 하나가 선택되고,

B는 Sb, As, Bi, 및 P를 포함하는 군으로부터 선택되고,

C는 S, Se, 및 Te를 포함하는 군으로부터 선택되며,

상기 상변화 물질막의 각 층의 조성이 상이하고, 상변화 온도가 서로 상이한 것인,

다층 상변화 물질막.

# 청구항 2

삭제

## 청구항 3

삭제

## 청구항 4

제 1 항에 있어서,

상기 분리막에 포함되는 상기 비옥사이드계 물질은, Ti, Ta, W, Hf, Zr, Ru, Mo, Co, Ni, Mn 및 이들의 질화물 또는 칼코겐화합물, 탄소계 물질, SiN, SiC, SiCN, AlN, BN (boron nitride), 및 CN (carbon nitride)로 이루어진 군으로부터 선택되는 것을 포함하는 것인, 다층 상변화 물질막.

# 청구항 5

제 1 항에 있어서,

상기 상변화 물질막의 각 층의 상변화 온도는 100℃ 내지 500℃ 범위인 것인, 다층 상변화 물질막.

#### 청구항 6

제 1 항에 있어서,

상기 상변화 물질막의 각 층의 상변화 온도는 상기 상변화 물질막의 각 층의 조성에 따라 조절되는 것인, 다층 상변화 물질막.

## 청구항 7

제 1 전극;

상기 제 1 전극에 형성되는 제 1 항, 제 4 항 내지 제 6 항 중 어느 한 항에 따른 다층 상변화 물질막; 및 상기 다층 상변화 물질막에 형성되는 제 2 전극

을 포함하는, 상변화 메모리 소자.

#### 청구항 8

제 7 항에 있어서,

상기 상변화 메모리 소자는 상기 다층 상변화 물질막을 포함함으로써 멀티레벨 코딩을 구현하는 것인, 상변화 메모리 소자.

#### 청구항 9

제 7 항에 있어서,

상기 제 1 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는, 상변화 메모리 소자.

# 청구항 10

제 9 항에 있어서,

상기 제 2 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는, 상변화 메모리 소자.

## 청구항 11

제 7 항에 있어서,

상기 다층 상변화 물질막의 각 층은 전기적 신호에 의해 상변화하는 것인, 상변화 메모리 소자.

## 청구항 12

기재(substrate)의 일부분에 형성된 제 1 전극;

상기 제 1 전극이 형성된 상기 기재에 형성되며, 상기 제 1 전극을 노출시키는 홀(hole)을 포함하는 절연막;

상기 홀 내의 노출된 상기 제 1 전극에 형성되는 제 1 항, 제 4 항 내지 제 6 항 중 어느 한 항에 따른 다층 상 변화 물질막; 및

상기 다층 상변화 물질막에 형성되는 제 2 전극

을 포함하는, 상변화 메모리 소자.

## 청구항 13

제 12 항에 있어서,

상기 상변화 메모리 소자는 상기 다층 상변화 물질막을 포함함으로써 멀티레벨 코딩을 구현하는 것인, 상변화 메모리 소자.

## 청구항 14

제 12 항에 있어서,

상기 제 1 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는, 상변화 메모리 소자.

### 청구항 15

제 14 항에 있어서,

상기 제 2 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는, 상변화 메모리 소자.

#### 청구항 16

제 12 항에 있어서,

상기 다층 상변화 물질막의 각 층은 전기적 신호에 의해 상변화하는 것인, 상변화 메모리 소자.

#### 청구항 17

상변화 물질막의 층을 형성하는 것;

상기 상변화 물질막의 층에 분리막을 형성하는 것; 및

상기 분리막에 상변화 물질막의 층을 형성하는 것

을 1회 이상 반복하여 수행하는 것

을 포함하는, 다층 상변화 물질막의 제조 방법으로서,

상기 다층 상변화 물질막은 상기 상변화 물질막의 각 층 사이에 형성된 분리막을 포함하며,

상기 분리막은 상기 상변화 물질막의 충들 사이의 원소 이동을 방지하는 것이고, 상기 분리막은 비옥사이드계 물질을 포함하는 것이고,

상기 상변화 물질막의 각 층은 A-B-C 상변화 물질을 포함하는 것이며,

상기 상변화 물질막의 각 층은,

A-B 막을 형성하는 단계; 및

상기 형성된 A-B막을 칼코겐 원소 C-함유 전구체를 포함하는 기체 분위기 하에서 어닐링하는 것에 의하여 상기 A-B 막을 칼코게나이드화함으로써 칼코겐-함유 A-B-C 막을 형성하는 단계를 통해 제조되는 것이고,

여기서, A는 Ge, Sn, Si, In, Al, Ag, 및 Ga를 포함하는 군으로부터 적어도 하나가 선택되고,

B는 Sb, As, Bi, 및 P를 포함하는 군으로부터 선택되고,

C는 S, Se, 및 Te를 포함하는 군으로부터 선택되며,

상기 상변화 물질막의 각 층의 조성이 상이하고, 상변화 온도가 서로 상이한 것인,

다층 상변화 물질막의 제조 방법.

#### 청구항 18

제 17 항에 있어서,

상기 상변화 물질막의 각 층 및 상기 분리막을 형성하는 것은 물리적 기상 증착법, 화학적 기상 증착법, 또는 원자층 증착법에 의해 수행되는 것인, 제 1 항, 제 4 항 내지 제 6 항 중 어느 한 항에 따른 다층 상변화 물질 막의 제조 방법.

#### 청구항 19

삭제

#### 청구항 20

삭제

#### 청구항 21

제 17 항에 있어서,

상기 분리막에 포함되는 상기 비옥사이드계 물질은, 구체적으로, Ti, Ta, W, Hf, Zr, Ru, Mo, Co, Ni, Mn 및 이들의 질화물 또는 칼코겐화합물, 탄소계 물질, SiN, SiC, SiCN, AlN, BN (boron nitride), 및 CN (carbon nitride)로 이루어진 군으로부터 선택되는 것을 포함하는 것인, 다층 상변화 물질막의 제조 방법.

### 청구항 22

제 17 항에 있어서,

상기 상변화 물질막의 각 층의 상변화 온도는 100℃ 내지 500℃ 범위인 것인, 다층 상변화 물질막의 제조 방법.

# 청구항 23

제 17 항에 있어서,

상기 상변화 물질막의 각 층의 상변화 온도는 상기 상변화 물질막의 각 층의 조성에 따라 조절되는 것인, 다층 상변화 물질막의 제조 방법.

# 발명의 설명

#### 기 술 분 야

[0001] 본원은, 다층 상변화 물질막 및 상기 다층 상변화 물질막의 제조 방법, 및 상기 다층 상변화 물질막을 포함하는 상변화 메모리 소자에 관한 것이다.

# 배경기술

[0002] 상변화 메모리 소자는 상변화 물질 층의 결정질/비정질 간 상변화에 따라 발생하는 저항의 차이를 이용하여 구동하기 때문에 이 두 가지 상태를 단일 비트(bit) 메모리의 1,0에 대응시켜서 상변화 메모리 소자를 구현할 수있다. 상변화 메모리 소자는 DRAM, SRAM과는 달리 전원이 꺼지더라도 저장된 정보가 보존되는 비휘발성 (nonvolatile) 메모리 소자로서 한번 기록된 정보는 70℃의 고온에서도 20년 이상 보존할 수 있으며, 우주복사선 및 전자기과 등에 영향을 받지 않아 우주공간에서도 본래의 기능대로 동작하는 것이 가능하고, 높은 내구성을 지뎌 1,000 회 이상 반복해서 정보를 읽고 지우는 것이 가능하다. 또한, 상변화 메모리의 주요 특성 중 하

나인 빠른 리드/엑세스(read/access) 시간은 현재 수 μs 수십 μs 단위의 특성을 보이는 비휘발성 메모리의 대표격인 플래쉬 메모리(flash memory) 보다 1,000 배 이상 빠른 수 ns 수십 ns에 이르며, SRAM과 같이 읽고 쓰기 시간이 매우 짧아 빠른 구동에 유리하다. 또한 동작 전압은 DRAM과 비슷한 수준인 2 V 내지 5 V 이하의 낮은 전압에서 동작이 가능하다. 그럼에도 불구하고 비교적 간단한 셀 구조를 가지기 때문에 소자 크기를 DRAM 수준까지 낮추는 것이 가능하여 집적화에 매우 유리하며, 독립형(stand-alone) 메모리는 물론 SoC 용 임베디드 (embeded) 메모리에도 적용 가능하다.

- [0003] 현재 PRAM의 핵심물질인 상변화 재료 중에 가장 보편적으로 쓰이는 물질은 Ge-Sb-Te 3원계 칼코게나이드 물질 (GST)이다. GST는 낮은 결정화 온도로 인한 셀 간 열 간섭 현상이 발생할 가능성이 있는 것으로 알려져 있으며, 용융 온도가 높기 때문에 비정질화(reset)를 위해 높은 전압의 리셋 펄스(reset pulse)가 필요하여 전력 소비적인 측면에서 단점을 지니고 있다. 또한, 집적화에 유리한 멀티-레벨 코딩(multi-level coding)의 어려움, 고집적화에 따른 리텐션(retention) 열화, 드리프트(drift) 현상 등 재료의 안정성에 있어 취약성이 있음이 알려져 있다. 따라서, 상전이 메모리 분야의 발전을 위해서는 미세화된 구조에서 저전류 동작이 가능하고, 상호간의 열 간섭의 최소화 및 열 간섭에 따른 각 상의 불안전 전이에 대해 안정적인 비정질 상태를 유지할 수 있는 상전이 물질 연구 및 새로운 구조의 연구가 진행되고 있다. 2010년 발표된 컨파인(confined) 구조의 상변화 메모리 셀은 가로 7.5 nm, 세로 17 nm, 및 깊이 30 nm의 홀을 형성하고 GST를 매립하여 셀 간의 간섭을 최소화 및 초고집적 메모리 소자를 제조할 수 있는 셀을 제작하였다.

- [0004] 하지만 상변화 물질층의 결정질/비정질 간 상변화에 따라 발생하는 저항의 차이를 이용하여 단일 비트인 1,0 만구현 하고 있다. 현재 NAND 플래쉬의 MLC(Multi level cell), TLC(Triple level cell)처럼 하나의 셀에 4개의 상태 정보(11,10,01,00) 또는 8 개의 상태 정보(111,110,101,100,011,010,001,000)를 상변화 메모리에 적용하기 위해서는 저항이 다른 4가지 상태 또는 8가지 상태를 이용하면 다중 비트 상변화 메모리 소자를 구성할 수 있다. 그러나, 현재 상변화 메모리의 핵심 물질인 GST는 용융 온도가 높아 비정질화(reset)를 위해 높은 전압의 리셋(결정화) 펄스가 필요하며, 조성이 다른 다층 GST의 구조에서 이러한 높은 전압의 리셋 펄스는 Ge-Sb-Te 원자의 결정질/비정질 간 상변화에 따라 조성이 섞이게 되어 집적화에 유리한 멀티-레벨 코딩의 장점을 잃게 된다.

- [0005] 또한, 비정질화 및 결정화를 위해 상부전극과 하부전극 사이에 전기장을 인가하는데 이 과정이 반복되면 초기 균일한 조성을 가지고 있던 GST 박막도 양이온 (Ge, Sb)과 음이온(Te)이 서로 다른 방향으로 이동하여 조성이 불균일해지는 현상이 발생하여 멀티-레벨 코딩의 장점을 잃게 된다 [IEDM 16, p. 83-86, ALD-based Confined PCM with a Metallic Liner toward Unlimited Endurance, W.Kim et al.].

- [0006] 한편, 대한민국 공개특허공보 제2008-0028544호는 컨파인드 셀 구조를 갖는 상변환 기억 소자 및 그의 제조방법에 대하여 개시하고 있다.

# 발명의 내용

## 해결하려는 과제

- [0007] 본원은, 다층 상변화 물질막 및 상기 다층 상변화 물질막의 제조 방법, 및 상기 다층 상변화 물질막을 포함하는 상변화 메모리 소자에 관한 것이다.

- [0008] 그러나, 본원이 해결하고자 하는 과제는 이상에서 언급한 과제로 제한되지 않으며, 언급되지 않은 또 다른 과제 들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

#### 과제의 해결 수단

- [0009] 본원의 제 1 측면은, 복수 층의 상변화 물질막; 및 상기 상변화 물질막의 각 층 사이에 형성된 분리막을 포함하며, 상기 분리막은 상기 상변화 물질막의 충들 사이의 원소 이동을 방지하는 것이고, 상기 분리막은 비옥사이드계 물질을 포함하는 것인, 다층 상변화 물질막을 제공한다.

- [0010] 본원의 제 2 측면은, 제 1 전극; 상기 제 1 전극에 형성되는 본원의 제 1 측면에 따른 다층 상변화 물질막; 및 상기 다층 상변화 물질막에 형성되는 제 2 전극을 포함하는, 상변화 메모리 소자를 제공한다.

- [0011] 본원의 제 3 측면은, 기재(substrate)의 일부분에 형성된 제 1 전극; 상기 제 1 전극이 형성된 상기 기재에 형성되며, 상기 제 1 전극을 노출시키는 홀(hole)을 포함하는 절연막; 상기 홀 내의 노출된 상기 제 1 전극에 형성되는 본원의 제 1 측면에 따른 다층 상변화 물질막; 및 상기 다층 상변화 물질막에 형성되는 제 2 전극을 포

함하는, 상변화 메모리 소자를 제공한다.

[0012] 본원의 제 4 측면은, 상변화 물질막의 층을 형성하는 것; 상기 상변화 물질막의 층에 분리막을 형성하는 것; 및 상기 분리막에 상변화 물질막의 층을 형성하는 것을 1회 이상 반복하여 수행하는 것을 포함하는, 다층 상변화물질막의 제조 방법으로서, 상기 다층 상변화물질막은 상기 상변화물질막의 각 층 사이에 형성된 분리막을 포함하며, 상기 분리막은 상기 상변화물질막의 충들 사이의 원소 이동을 방지하는 것이고, 상기 분리막은 비옥사이드계물질을 포함하는 것인, 다층 상변화물질막의 제조 방법을 제공한다.

# 발명의 효과

- [0013] 본원의 일 구현예에 따른 다층 상변화 물질막은, 상변화 물질들 사이에 전기 전도도가 높거나 부도체인 비옥사이드계 물질을 포함하는 분리막을 포함함으로써 전압 인가에 따른 반복적인 상변화에도 상기 분리막에 의해 충간 원소 이동이 방지되고, 위충 및 아래충의 조성이 섞이는 것을 방지할 수 있는 효과가 있으며, 이에 따라 멀티 레벨 특성을 유지할 수 있다.

- [0014] 본원의 일 구현예에 따른 다층 상변화 물질막이 조성이 상이한 다층의 상변화 물질층들을 포함하는 경우, 각 층 마다 상이한 결정화 온도를 가짐으로써 멀티 코딩(multi coding)이 가능한 특성이 있다.

#### 도면의 간단한 설명

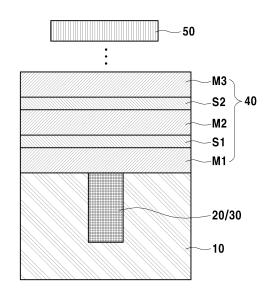

- [0015] 도 1은, 종래의 분리막이 없는 상변화 다층막 구조 메모리 소자의 시간의 흐름에 따른 상변화 다층막 조성 변화를 나타내는 모식도이다.

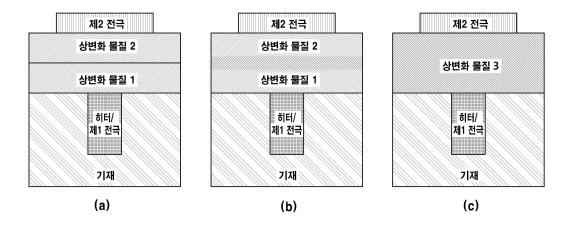

- 도 2는, 본원의 일 구현예에 따른 분리막을 포함하는 다층 상변화 물질막을 포함하는 메모리 소자의 모식도이다.

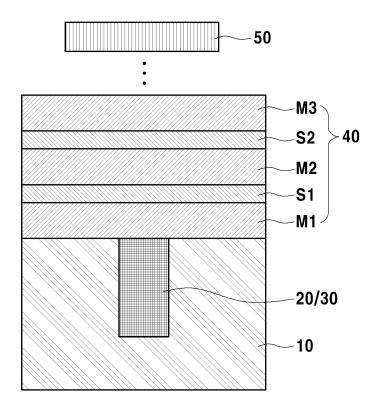

- 도 3은, (a) 종래의 컨파인드 구조 다층막 및 (b) 본원의 일 구현예에 따른 분리막을 포함하는 다층 상변화 물질막 메모리 소자의 모식도이다.

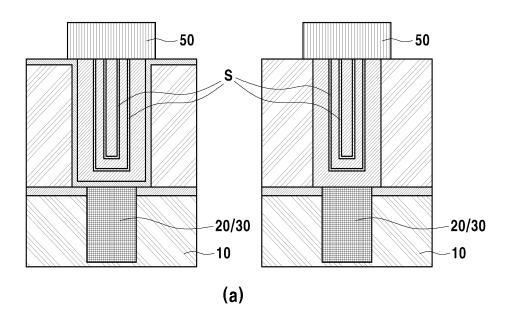

- 도 4는, (a) 종래의 단일층 상변화 물질막 및 (b) 본원의 일 구현예에 따른 분리막을 포함하는 다층 상변화 물질막의 메모리 소자의 온도에 따른 저항 변화 그래프이다.

도 5는, 본원의 일 구현예에 따른 분리막을 포함하는 다층 상변화 물질막을 포함하는 메모리 소자 제조 시 사용될 수 있는 다양한 상변화 물질에 대한 온도-저항 관계 그래프이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0016] 이하, 첨부한 도면을 참조하여 본원이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 본원의 실시예를 상세히 설명한다. 그러나 본원은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다. 그리고 도면에서 본원을 명확하게 설명하기 위해서 설명과 관계없는 부분은 생략하였으며, 명세서 전체를 통하여 유사한 부분에 대해서는 유사한 도면 부호를 붙였다.

- [0017] 본원 명세서 전체에서, 어떤 부분이 다른 부분과 "연결"되어 있다고 할 때, 이는 "직접적으로 연결"되어 있는 경우뿐 아니라, 그 중간에 다른 소자를 사이에 두고 "전기적으로 연결"되어 있는 경우도 포함한다.

- [0018] 본원 명세서 전체에서, 어떤 부재가 다른 부재 "상에" 위치하고 있다고 할 때, 이는 어떤 부재가 다른 부재에 접해 있는 경우뿐 아니라 두 부재 사이에 또 다른 부재가 존재하는 경우도 포함한다.

- [0019] 본원 명세서 전체에서, 어떤 부분이 어떤 구성 요소를 "포함"한다고 할 때, 이는 특별히 상대되는 기재가 없는 한 다른 구성 요소를 제외하는 것이 아니라 다른 구성 요소를 더 포함할 수 있는 것을 의미한다.

- [0020] 본원 명세서 전체에서 사용되는 정도의 용어 "약", "실질적으로" 등은 언급된 의미에 고유한 제조 및 물질 허용 오차가 제시될 때 그 수치에서 또는 그 수치에 근접한 의미로 사용되고, 본원의 이해를 돕기 위해 정확하거나 절대적인 수치가 언급된 개시 내용을 비양심적인 침해자가 부당하게 이용하는 것을 방지하기 위해 사용된다.

- [0021] 본원 명세서 전체에서 사용되는 정도의 용어 "~(하는) 단계" 또는 "~의 단계"는 "~를 위한 단계"를 의미하지 않는다.

- [0022] 본원 명세서 전체에서, 마쿠시 형식의 표현에 포함된 "이들의 조합(들)"의 용어는 마쿠시 형식의 표현에 기재된 구성 요소들로 이루어진 군에서 선택되는 하나 이상의 혼합 또는 조합을 의미하는 것으로서, 상기 구성 요소들

로 이루어진 군에서 선택되는 하나 이상을 포함하는 것을 의미한다.

- [0023] 본원 명세서 전체에서, "A 및/또는 B"의 기재는, "A 또는 B, 또는 A 및 B"를 의미한다.

- [0024] 본원 명세서 전체에서, "알킬기"는, 각각, 선형 또는 분지형의, 포화 또는 불포화의 C<sub>1-6</sub> 알킬기를 포함하는 것일 수 있으며, 예를 들어, 메틸, 에틸, 프로필, 부틸, 펜틸, 헥실, 또는 이들의 가능한 모든 이성질체를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0025] 본원 명세서 전체에서, 용어 "알콕시기"는 앞서 정의된 상기 알킬기가 산소 원자와 연결된 것으로서, 예를 들어, 메톡시, 에톡시, 프로폭시, 부톡시, 펜톡시, 헥실옥시, 또는 이들의 가능한 모든 이성질체를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0026] 본원 명세서 전체에서, 용어 "알킬아민기"는 하나 또는 두개의 알킬기(R)에 의해 치환된 아미노기 (-NHR 또는-NRR'; 여기서, R 및 R'는 서로 독립적일 수 있고, 또는 동일할 수 있음)를 의미하는 것으로서, 상기 알킬기는 앞서 정의된 것과 같다. 예를 들어, 상기 알킬아민기는 메틸아미노, 에틸아미노, n-프로필아미노, 이소프로필아미노, n-부틸아미노, 2-부틸아미노, 이소-부틸아미노, tert-부틸아미노, 디메틸아미노, 디에틸아미노, 디프로 필아미노, 디부틸아미노, 메틸-에틸-아미노, 메틸-프로필-아미노, 메틸-이소프로필아미노, 메틸-부틸-아미노, 메틸-이소부틸-아미노, 메틸-이소부틸-아미노, 에틸-이소부틸-아미노, 에틸-이소부틸-아미노, 어틸-이소부틸-아미노, 등을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0027] 본원 명세서 전체에서, "막"은 "박막"을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0028] 본원 명세서 전체에서, "X" 또는 "할로겐 또는 할라이드"는 주기율표의 17 족에 속하는 할로겐 원자가 작용기의 형태로서 화합물에 포함되어 있는 것을 의미하는 것으로서, 예를 들어, 상기 할로겐 원자는 염소, 브롬, 불소 또는 요오드일 수 있으나, 이에 제한되지 않을 수 있다.

- [0030] 이하, 본원의 구현예를 상세히 설명하였으나, 본원이 이에 제한되지 않을 수 있다.

- [0032] 본원의 제 1 측면은, 복수 층의 상변화 물질막; 및 상기 상변화 물질막의 각 층 사이에 형성된 분리막을 포함하며, 상기 분리막은 상기 상변화 물질막의 층들 사이의 원소 이동을 방지하는 것이고, 상기 분리막은 비옥사이드 계 물질을 포함하는 것인, 다층 상변화 물질막을 제공한다.

- [0033] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 상변화 온도가 서로 동일하거나 상이한 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0034] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층은 A-B-C 상변화 물질을 포함하는 것이며, 여기서 A는 Ge, Sn, Si, In, Al, Ag, 및 Ga를 포함하는 군으로부터 적어도 하나가 선택되고, B는 Sb, As, Bi, 및 P를 포함하는 군으로부터 선택되고, C는S, Se, 및Te를 포함하는 군으로부터 선택되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 A-B-C 상변화 물질은 Ge-Sb-Te 계열, In-Sb-Te계열, Sn-Sb-Se 계열 등일 수 있으나 이에 제한되지 않는다.

- [0035] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층은 A-B-C 상변화 물질층 형성 후 도핑되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 도핑은 N-, C-, 또는 Si-도핑을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0036] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 두께는 서로 동일하거나 상이할 수 있으며, 상기 상변화 각 층의 두께는 특별히 제한되지 않으며, 원하는 상변화 물질막의 제조를 위해 설계자에 의해 자유롭게 변경될 수 있다.

- [0037] 본원의 일 구현예에 있어서, 상기 상변화 물질막 각 층의 두께는 각각 독립적으로 약 0.1 nm 내지 약 50 nm인 것일 수 있으나, 이에 제한되지 않는다. 예를 들어, 상기 상변화 물질막 각 층의 두께는 약 0.1 nm 내지 약 50 nm, 약 1 nm 내지 약 50 nm, 약 10 nm 내지 약 50 nm, 약 20 nm 내지 약 50 nm, 약 30 nm 내지 약 50 nm, 약 40 nm, 약 50 nm, 약 40 nm, 약 50 nm, 약 40 nm, 약 30 nm 내지 약 40 nm, 약 30 nm 내지 약 40 nm, 약 1 nm 내지 약 30 nm, 약 10 nm 내지 약 20 nm, 약 0.1 nm 내지 약 10 nm, 약 10 nm 내지 약 20 nm, 약 1 nm 내지 약 20 nm, 약 10 nm 내지 약 20 nm, 약 10 nm 내지 약 10 nm, 약 10 nm, 약 10 nm, 또는 약 0.1 nm 내지 약 1 nm인 것일 수 있으나, 이에 제한되지 않는다.

- [0038] 본원의 일 구현예에 있어서, 상기 분리막에 포함되는 상기 비옥사이드계 물질은, 구체적으로, Ti, Ta, W, Hf,

Zr, Ru, Mo, Co, Ni, Mn 및 이들의 질화물 또는 칼코겐화합물, 탄소계 물질, SiN, SiC, SiCN, AlN, BN (boron nitride), 및 CN (carbon nitride)로 이루어진 군으로부터 선택되는 것을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 상기 탄소계 물질은, 예를 들어, 탄소, CNT, 또는 그래핀 등을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 상기 칼코겐 화합물은 본 기술 분야에 공지된 것들을 특별히 제한 없이 사용될 수 있으며, 예를 들어, 전이금속 칼코겐 화합물(Transition Metal Dichalcogenide: TMDC)을 사용할 수 있으며, 구체적으로, MoS2, WS2, MoSe2, WSe2, MoTe2 또는 MoSe2의 전이금속 칼코겐 화합물을 사용할 수 있으나, 이에 제한되는 것은 아니다. 상기 분리막의 간격은 적충되는 상변화 물질막의 두께에 따라 결정되며 상기 분리막의 두께는 상변화 특성에 따라 설계자에 의해 자유롭게 변경 할 수 있다.

- [0039] 본원의 일 구현예에 있어서, 상기 분리막은 상기 상변화 물질막의 충들 사이의 원소 이동을 방지하는 것으로서, 비옥사이드계 물질의 전기 전도성 물질 또는 부도체를 포함하는 것이고, 절연막은 제외되는 것일 수 있다. 이는, 절연막에 포함되는 산소 성분은 메모리 소자에 좋지 않은 영향을 끼칠 수 있기 때문이다.

- [0040] 본원의 일 구현예에 있어서, 상기 분리막 각 층의 두께는 서로 동일하거나 상이할 수 있으며, 상기 분리막 각 층의 두께는 특별히 제한되지 않으며, 원하는 상변화 물질막의 제조를 위해 설계자에 의해 자유롭게 변경될 수 있다.

- [0041] 본원의 일 구현예에 있어서, 상기 분리막 각 층의 두께는 각각 독립적으로 약 0.1 nm 내지 약 10 nm인 것일 수 있으나, 이에 제한되지 않는다. 예를 들어, 상기 분리막 각 층의 두께는 약 0.1 nm 내지 약 10 nm, 약 0.1 nm 내지 약 5 nm, 약 0.1 nm 내지 약 3 nm, 약 0.1 nm 내지 약 1 nm, 약 1 nm 내지 약 10 nm, 약 1 nm 내지 약 5 nm, 또는 약 1 nm 내지 약 3 nm 일 수 있으나, 이에 제한되지 않는다.

- [0042] 본원의 일 구현예에 있어서, 상기 상변화 물질막 각 층의 두께와 상기 분리막 각 층의 두께는 서로 동일하거나 상이할 수 있으며, 상기 두께는 특별히 제한되지 않는다. 예를 들어, 세 층의 상변화 물질막과 두 층의 상기 분리막을 갖는 경우, 상변화 물질 1 및 상변화 물질 2 사이의 분리막 두께는 약 2 nm, 상변화 물질 2 및 상변화물질 3 사이의 분리막 두께는 약 5 nm일 수 있으나, 이에 제한되지 않는다.

- [0043] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 상변화 온도(결정화 온도)는 약 100℃ 내지 약 500 ℃ 범위인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 상변화 물질막의 각 층의 상변화 온도(결정화 온도)는 약 100℃ 내지 약 500℃, 약 100℃ 내지 약 400℃, 약 100℃ 내지 약 300℃, 약 100℃ 내지 약 500℃ 내지 약 500℃ 내지 약 400℃, 약 200℃ 내지 약 300℃, 약 300℃ 내지 약 500 ℃, 약 300℃ 내지 약 400℃, 또는 약 400℃ 내지 약 500℃ 범위인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 세 층의 상변화 물질막과 두 층의 상기 분리막을 갖는 경우, 상기 상변화 물질막의 각 층의 상변화는, 약 100℃, 약 120℃, 및 약 140℃에서 순차적으로 상변화가 일어나는 것일 수 있으나, 이에 제한되지 않는다. 본원의 일 구현예에 있어서, 상기 상변화 물질막들의 조성이 각각 상이한 경우, 각 층의 상변화 온도가 점진적으로 증가하거나 점진적으로 감소하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0044] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 상변화 온도는 상기 상변화 물질막의 각 층의 조성에 따라 조절되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0046] 본원의 제 2 측면은, 제 1 전극; 상기 제 1 전극에 형성되는 본원의 제 1 측면에 따른 다층 상변화 물질막; 및 상기 다층 상변화 물질막에 형성되는 제 2 전극을 포함하는, 상변화 메모리 소자를 제공한다.

- [0047] 상기 본원의 제 1 측면의 다층 상변화 물질막에 대한 내용의 중복 기재를 생락하였으나 본 측면에 대하여 모두 적용될 수 있다.

- [0048] 본원의 일 구현예에 있어서, 상기 상변화 메모리 소자는 상기 다층 상변화 물질막을 포함함으로써 멀티레벨 코딩을 구현하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0049] 본원의 일 구현예에 있어서, 상기 제 1 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터(heater)를 추가 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0050] 본원의 일 구현예에 있어서, 상기 제 2 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0051] 본원의 일 구현예에 있어서, 상기 히터는 금속 재료 및 이의 화합물, 이의 산화물 또는 이의 질화물를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0052] 본원의 일 구현예에 있어서, 상기 다층 상변화 물질막의 각 층은 전기적 신호에 의해 상변화하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0053] 본원의 일 구현예에 있어서, 상기 전기적 신호는 약 1 mV 내지 약 20 V 범위의 전압이거나, 또는 약 1 nA 내지 약 1 A 범위의 전류인 것일 수 있으며, 또한, 상기 전기적 신호는 약 1 ns 내지 약 1 ms 범위의 펼스인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0054] 예를 들어, 상기 전기적 신호는 약 1 mV 내지 약 20 V, 약 1 mV 내지 약 10 V, 약 1 mV 내지 약 5 V, 약 1 mV 내지 약 1 V, 약 1 mV 내지 약 500 mV, 약 1 mV 내지 약 100 mV, 또는 약 1 mV 내지 약 50 mV 범위의 전압일수 있으며, 또는 상기 전기적 신호는 약 1 nA 내지 약 1 A, 약 1 nA 내지 약 100 mA, 약 1 nA 내지 약 10 mA, 약 1 nA 내지 약 100 mA, 약 1 nA 내지 약 10 mA, 약 100 mA, 약 100 mA, 약 100 mA, 약 100 mA 내지 약 100 mA, 또는 약 10 mA 내지 약 1 A범위의 전류인 것일 수 있으나, 이에 제한되지 않는다.

- [0055] 예를 들어, 상기 전기적 신호는 약 1 ns 내지 약 1 ms, 약 1 ns 내지 약 100 μs, 약 1 ns 내지 약 10 μs, 약 1 ns 내지 약 1 μs, 약 1 ns 내지 약 1 ns 내지 약 10 ns, 약 1 ns 내지 약 10 ns, 약 10 ns 내지 약 1 ms, 약 100 ns 내지 약 100 μs, 약 100 ns 내지 약 10 μs, 약 100 ns 내지 약 1 μs, 약 1 μs 내지 약 1 ms, 약 1 μs 내지 약 1 ms, 약 10 μs 내지 약 1 ms, 약 10 μs 내지 약 1 ms, 약 10 μs 내지 약 100 μs, 또는 약 100 μs 내지 약 1 ms 범위의 펼스인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0057] 본원의 제 3 측면은, 기재(substrate)의 일부분에 형성된 제 1 전극; 상기 제 1 전극이 형성된 상기 기재에 형성되며, 상기 제 1 전극을 노출시키는 홀(hole)을 포함하는 절연막; 상기 홀 내의 노출된 상기 제 1 전극에 형성되는 본원의 제 1 측면에 따른 다층 상변화 물질막; 및 상기 다층 상변화 물질막에 형성되는 제 2 전극을 포함하는, 상변화 메모리 소자를 제공한다.

- [0058] 상기 본원의 제 1 측면의 다층 상변화 물질막에 대한 내용의 중복 기재를 생락하였으나 본 측면에 대하여 모두 적용될 수 있다.

- [0059] 본원의 일 구현예에 있어서, 상기 상변화 메모리 소자는 상기 다층 상변화 물질막을 포함함으로써 멀티레벨 코딩을 구현하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0060] 본원의 일 구현예에 있어서, 상기 상변화 메모리 소자는 상기 홀 내의 노출된 상기 제 1 전극에 가로 방향으로 형성된 상기 다층 상변화 물질막을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0061] 본원의 일 구현예에 있어서, 상기 제 1 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0062] 본원의 일 구현예에 있어서, 상기 제 2 전극과 상기 다층 상변화 물질막 사이에 위치하는 히터를 추가 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0063] 본원의 일 구현예에 있어서, 상기 히터는 금속 재료 및 이의 화합물, 이의 산화물 또는 이의 질화물를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0064] 본원의 일 구현예에 있어서, 본 측면에 따른 상변화 메모리 소자는 컨파인드(confined) 구조를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0065] 본원의 일 구현예에 있어서, 상기 다층 상변화 물질막의 각 층은 전기적 신호에 의해 상변화하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0066] 본원의 일 구현예에 있어서, 상기 전기적 신호는 약 1 mV 내지 약 20 V 범위의 전압이거나, 또는 약 1 nA 내지 약 1 A 범위의 전류인 것일 수 있으며, 또한, 상기 전기적 신호는 약 1 ns 내지 약 1 ms 범위의 펼스인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0067] 예를 들어, 상기 전기적 신호는 약 1 mV 내지 약 20 V, 약 1 mV 내지 약 10 V, 약 1 mV 내지 약 5 V, 약 1 mV 내지 약 1 V, 약 1 mV 내지 약 500 mV, 약 1 mV 내지 약 100 mV, 또는 약 1 mV 내지 약 50 mV 범위의 전압일수 있으며, 또는 상기 전기적 신호는 약 1 nA 내지 약 1 A, 약 1 nA 내지 약 100 mA, 약 1 nA 내지 약 10 mA,

- [0068] 예를 들어, 상기 전기적 신호는 약 1 ns 내지 약 1 ms, 약 1 ns 내지 약 100 μs, 약 1 ns 내지 약 10 μs, 약 1 ns 내지 약 1 μs, 약 1 ns 내지 약 10 ns, 약 1 ns 내지 약 10 ns, 약 10 ns 내지 약 1 μs, 약 1 μs 내지 약 100 μs, 약 1 μs 내지 약 100 μs, 약 10 μs 내지 약 100 μs, 약 10 μs 내지 약 100 μs, 약 100 μs, 약 100 μs 내지 약 1 ms, 약 10 μs 내지 약 100 μs, 또는 약 100 μs 내지 약 1 ms 범위의 펄스인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0070] 본원의 제 4 측면은, 상변화 물질막의 층을 형성하는 것; 상기 상변화 물질막의 층에 분리막을 형성하는 것; 및 상기 분리막에 상변화 물질막의 층을 형성하는 것을 1회 이상 반복하여 수행하는 것을 포함하는, 다층 상변화 물질막의 제조 방법으로서, 상기 다층 상변화 물질막은 상기 상변화 물질막의 각 층 사이에 형성된 분리막을 포함하며, 상기 분리막은 상기 상변화 물질막의 현돌 사이의 원소 이동을 방지하는 것이고, 상기 분리막은 비옥사이드계 물질을 포함하는 것인, 다층 상변화 물질막의 제조 방법을 제공한다.

- [0071] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층 및 상기 분리막을 형성하는 것은 물리적 기상 증착법, 화학적 기상 증착법(CVD), 및/또는 원자층 증착법(ALD)에 의해 수행되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0072] 본원의 일 구현예에 있어서, 상기 물리적 기상 증착법은 증발법, 스퍼터링, 또는 펄스 레이저 증착을 포함하는 것일 수 있으며, 상기 화학적 기상 증착법은 저압 화학기상증착법, 상압 화학기상증착법, 금속 유기 화학기상증 착법, 플라즈마 화학기상증착법, 또는 유도결합 플라즈마 증착법을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0073] 본원의 일 구현예에 있어서, 상기 원자층 증착법(ALD)은 피복성이 우수하고 원자층 단위로 두께 조절이 가능하며, CVD와 혼용할 경우 미세 직경 및 홀을 갖는 기재의 홀의 매립을 안정적으로 수행할 수 있다.

- [0074] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층 및 상기 분리막의 형성 온도는 상온 내지 약 400℃ 범위인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 상변화 물질막의 각 층 및 상기 분리막은 상은 내지 약 400℃, 약 100℃ 내지 약 400℃, 약 200℃ 내지 약 400℃, 약 300℃, 약 300℃, 약 100℃ 내지 약 300℃, 약 200℃ 내지 약 300℃, 상은 내지 약 200℃, 또는 약 100℃ 내지 약 200℃ 인의 온도 범위에서 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0075] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 상변화 온도가 서로 동일하거나 상이한 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0076] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층은 A-B-C 상변화 물질을 포함하는 것이며, 여기서, A는 Ge, Sn, Si, In, Al, Ag, 및 Ga를 포함하는 군으로부터 적어도 하나가 선택되고, B는 Sb, As, Bi, 및 P 를 포함하는 군으로부터 선택되고, C는 S, Se, 및 Te를 포함하는 군으로부터 선택되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0077] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층은 A-B-C 상변화 물질층 형성 후 도핑되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 도핑은 N-, C-, 또는 Si-도핑을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0078] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 제조는, A-B 상변화 물질막을 먼저 중착 후 상기 A-B 상변화물질막을 칼코게나이드화함으로써 제조될 수 있으며, 이러한 방법을 이용하여 각 층의 상변화물질막의 조성을 상이하게 조절할 수 있으나, 이에 제한되지 않는다. 상기 방법은, 구체적으로, A-B 막을 형성하는 단계; 및 상기 제조된 A-B 막을 칼코겐 원소 C-함유 전구체를 포함하는 기체 분위기 하에서 어닐링하는 것에 의하여 상기 A-B 막을 칼코게나이드화함으로써 A-B-C 상변화물질막을 형성하는 단계를 포함하며, 여기서 A는 Ge, Sn, Si, In, Al또는 Ga을 포함하고, B는 Sb, As, Bi, 또는 P를 포함하는 것일 수 있다.

- [0079] 본원의 일 구현예에 있어서, 상기 A-B 막을 형성하는 것은 약 80℃ 내지 약 300℃의 온도 범위에서 수행되는 것 일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어 상기 상기 A-B 막을 형성하는 것은 약 80℃ 내지 약

- [0080] 본원의 일 구현예에 있어서, 상기 칼코겐 원소 C는 S, Se, 또는Te를 포함하는 것일 수 있다.

- [0081] 본원의 일 구현예에 있어서, 상기 칼코겐 원소 C-함유 전구체는 수소, 알킬기, 아민기, 알킬아민기, 알콕시기, 실릴기, 게르밀기, 및 이들의 조합들로 이루어진 군에서 선택되는 치환기를 함유하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0082] 상기 칼코겐 원소 C-함유 전구체의 구체적인 예로는, H₂S, H₂Te, H₂Se, Te-(CH₃)₂, Te-(C₂H₅)₂, Te-(¹C₃H₁)₂, Te-(¹C₃H₁)₂, Te-(¹C₄H₂)₂, Te-(°C₂H₅)₂, Te-(°C₂Hҕ)₂, Te-(°C₂Hҕ)₂, Te-(°C₂Hҕ)₂, Te-(°C₂Hҕ)₂, Te-(°C₃H₁)₂, Te-(

- [0083] 본원의 일 구현예에 있어서, 상기 칼코겐 원소 C-함유 전구체를 포함하는 기체 분위기는 약 0.001 Torr 내지 약 760 Torr의 압력 범위에서 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 칼코겐 원소 C-함유 전구체를 포함하는 기체 분위기는 약 0.001 Torr 내지 약 760 Torr, 약 0.01 Torr 내지 약 760 Torr, 약 0.1 Torr 내지 약 760 Torr, 약 1 Torr 내지 약 760 Torr, 약 100 Torr 내지 약 760 Torr, 약 300 Torr 내지 약 760 Torr, 약 500 Torr, 약 500 Torr, 약 0.01 Torr 내지 약 300 Torr, 약 0.01 Torr 내지 약 300 Torr, 약 0.01 Torr 내지 약 300 Torr, 약 0.01 Torr 내지 약 100 Torr의 압력 범위에서 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0084] 본원의 일 구현예에 있어서, 상기 칼코겐 원소 C-함유 전구체를 포함하는 기체는 불활성 기체, 예를 들어, 아르 곤이나 헬륨 기체, 또는 N<sub>2</sub> 를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0085] 본원의 일 구현예에 있어서, 상기 칼코겐 원소 C-함유 전구체를 포함하는 기체 중 상기 칼코겐 원소 C-함유 전구체의 분압이 약 0.001 Torr 내지 약 100 Torr인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 칼코겐 원소 C-함유 전구체를 포함하는 기체 중 상기 칼코겐 원소 C-함유 전구체의 분압은 약 0.001 Torr 내지 약 100 Torr, 약 0.001 Torr 내지 약 50 Torr, 약 0.001 Torr 내지 약 30 Torr, 약 0.001 Torr 내지 약 10 Torr, 약 0.001 Torr 내지 약 1.0 Torr, 약 0.001 Torr 내지 약 1.0 Torr, 약 0.01 Torr 내지 약 1.0 Torr, 약 1.0 Torr, 약 1.0 Torr, 약 1.0 Torr, 약 1.0 Torr 내지 약 1.0 Torr, 약 1.0 Torr 내지 약 1.0 Torr, 약 1.0 Torr 내지 약 1.0 Torr 내지 약 3.0 Torr, 약 3.0 Torr, 약 1.0 Torr 내지 약 3.0 Torr, 약 3.0 Torr 내지 약 1.0 Torr 내지 약 3.0 Torr, 약 3.0 Torr 내지 약 1.0 Torr 내지 약 5.0 Torr, 또는 5.0 Torr 내지 약 1.0 Torr인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0086] 본원의 일 구현예에 있어서, 상기 어닐링은, 상기 형성된 A-B 막을 칼코겐 원소-함유 전구체를 포함하는 기체 분위기 하에서 증착 온도와 같거나 더 높은 온도에서 어닐링하는 것에 의하여 칼코게나이드화 시키는 것일 수 있으며, 약 100℃ 내지 약 500℃의 온도 범위에서 수행되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 어닐링은 약 100℃ 내지 약 500℃, 약 100℃ 내지 약 400℃, 약 100℃ 내지 약 300℃, 약 150℃ 내지 약 200℃, 약 150℃ 내지 약 500℃, 약 150℃ 내지 약 500℃, 약 200℃ 내지 약 300℃, 약 300℃ 내지 약 500℃, 약 200℃ 내지 약 500℃, 약 200℃ 내지 약 500℃, 약 300℃ 내지 약 500℃,

약 300°C 내지 약 400°C, 또는 약 400°C 내지 약 500°C의 온도 범위에서 수행되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0087] 본원의 일 구현예에 있어서, 상기 어닐링에 의해 상기 A-B 막에서 상변화가 일어날 수 있으며, 칼코게나이드화 과정에서 칼코겐 원소가 A-B 막으로 침투함에 따라 A-B 막의 부피가 팽창하기 때문에 비정질의 A-B 막이 결정화하는 경우에 부피 축소 현상에 의해 발생할 수 있는 보이드(void) 형성을 억제할 수 있으나, 이에 제한되지 않을 수 있다.

- [0088] 본원의 일 구현예에 있어서, 상기 어닐링에 의해 상기 A-B 막 전체 또는 상부가 칼코게나이드화되어 A-B-C 상변화 물질막이 형성되고 결정화 되는 것일 수 있으나, 이에 제한되지 않을 수 있다. 또한, 상기 어닐링에 의해 상기 A-B-C 상변화 물질막의 불순물이 제거되고 치밀화될 수 있는 효과가 있다. 상기 결정화에 따라 형성된 결정 구조는 육방정계(hexagonal) 또는 면심입방(face centered cubic) 결정 구조를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있으며, 특히 상기 육방정계(hexagonal) 결정 구조는 본원에 따른 상기 A-B-C 상변화 물질막에 대하여 열역학적으로 가장 안정한(stable) 구조일 수 있으나, 이에 제한되지 않을 수 있다.

- [0089] 본원의 일 구현예에 있어서, 상기 A-B 막의 형성은, A-함유 전구체 및 B-함유 전구체 간의 직접적인 화학 반응에 의한 것, 또는 A-함유 전구체의 환원과 B-함유 전구체의 환원에 의한 것, 또는 A-함유 전구체의 열분해와 B-함유 전구체의 열분해에 의한 것, 또는 이들의 조합에 의한 것이며, 상기 반응은 반복 수행될 수 있는 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 A-함유 전구체 및 B-함유 전구체 간의 직접적인 화학 반응은 원자 중착법에 의해 A-함유 전구체 및 B-함유 전구체를 순차적으로 교대로 주입하는 것일 수 있으며, 상기 A-함유 전구체의 환원과 B-함유 전구체의 환원에 의한 것은 원자 중착법에 의해 A-함유 전구체의 증착 후 환원제 주입 및 B-함유 전구체를 중착 후 환원제 주입을 순차적으로 교대로 수행하는 것일 수 있으며, 상기 A-함유 전구체의 열분해와 B-함유 전구체의 열분해에 의한 것은 화학 기상 중착에 의해 A-함유 전구체 및 B-함유 전구체를 순차적으로 교대로 주입하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0090] 본원의 또 다른 일 구현예에 있어서, 상기 A-B막의 형성에 사용되는 상기 전구체들중, 상기 A-함유 전구체는 시클로펜타디에닐(Cp), 알킬기, 아민기, 알킬아민기, 알콕시기, 할라이드, 및 이들의 조합들로 이루어진 군에서 선택되는 치환기를 포함하는 것이며, 상기 B-함유 전구체는 Si-함유 치환기, Ge-함유 치환기, 및 이들의 조합으로부터 선택되는 치환기를 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0091] 본원의 일 구현예에 있어서, 상기 A-함유 전구체는 ACpn, ARn, AHnR4-n, A(NR2)-n, A(OR)-n, AXn, AHnX4-n, AXn-다이옥산(1,4-dioxane), 및 이들의 조합들로 이루어진 군에서 선택되는 것을 포함하고 (X는 할로겐임), 상기 B-함유전구체는 B-(SiR3)m, B-[Si(NR2)3]m, B-(GeR3)m, B-[Ge(NR2)3]m, 및 이들의 조합들로 이루어진 군에서 선택되는 것 포함하는 것이며, 상기 R은 각각 독립적으로 탄소수 1 내지 6의 알킬기 또는 이들의 모든 가능한 이성질체를 포함하고, n 및 m은 각각 독립적으로 1 내지 4의 정수인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0092] 예를 들어, 상기 A-함유 전구체는 GeCp<sub>2</sub>, GeR<sub>4</sub>, GeH<sub>y</sub>R<sub>4-y</sub>, Ge(NR<sub>2</sub>)-<sub>4</sub>, Ge(OR)-<sub>4</sub>, GeX<sub>4</sub>, GeH<sub>y</sub>X<sub>4-y</sub>, GeX<sub>2</sub>-다이옥산 (1,4-dioxane), 및 이들의 조합들로 이루어진 군에서 선택되는 것을 상기 화학 반응에 이용하고, 더 구체적으로, 상기 A-함유 전구체는 GeCp<sub>2</sub>, Ge(CH<sub>3</sub>)<sub>4</sub>, Ge(C<sub>2</sub>H<sub>5</sub>)-<sub>4</sub>, Ge(<sup>i</sup>C<sub>3</sub>H<sub>7</sub>)-<sub>4</sub>, Ge[N-(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>, Ge[N-(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>]<sub>4</sub>, Ge(O-CH<sub>3</sub>)<sub>4</sub>, Ge(O-C<sub>2</sub>H<sub>5</sub>)<sub>4</sub>, Ge(O-(<sup>i</sup>C<sub>3</sub>H<sub>7</sub>)<sub>4</sub>), GeCl<sub>2</sub>-다이옥산, GeCl<sub>4</sub>, 또는 GeF<sub>4</sub> 등을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 여기서, 상기 R은 각각 독립적으로 탄소수 1 내지 6의 알킬기 또는 이들의 모든 가능한 이성질체를 포함하고, y는 1내지 4의 정수인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0093] 예를 들어, 상기 B-함유 전구체는 Sb-[Si-(CH<sub>3</sub>)-<sub>3</sub>]<sub>3</sub>, Sb-[Si-(C<sub>2</sub>H<sub>5</sub>)-<sub>3</sub>]<sub>3</sub>, Sb-[Si-(<sup>i</sup>C<sub>3</sub>H<sub>7</sub>)-<sub>3</sub>]<sub>3</sub>, Sb-(Si-[N-(CH<sub>3</sub>)<sub>2</sub>]<sub>3</sub>)<sub>3</sub>, Sb-(Si-[N-(CH<sub>3</sub>)<sub>2</sub>]<sub>3</sub>)<sub>3</sub>, Sb-[Ge-(CH<sub>3</sub>)-<sub>3</sub>]<sub>3</sub>, Sb-[Ge-(CH<sub>3</sub>)-<sub>3</sub>]<sub>3</sub>, Sb-(Ge-[N-(CH<sub>3</sub>)<sub>2</sub>]<sub>3</sub>)<sub>3</sub>, 또는 Sb-(Ge-[N-(CH<sub>3</sub>)<sub>2</sub>]<sub>3</sub>)<sub>3</sub>, 등을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0094] 본원의 일 구현예에 있어서, 복수개의 알킬기를 포함하는 상기 전구체는 각각 서로 동일하거나 상이할 수 있다.

- [0095] 본원의 일 구현예에 있어서, 상기 A-B-C 상변화 물질막의 제조 방법에 의해 제조된 상기 A-B-C 상변화 물질막은 미세 단차가 형성된 기재 또는 표면에서 형성되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0096] 본원의 일 구현예에 있어서, 상기 A-B 막을 형성하는 단계는 A 원료기체와 B원료기체 각각의 종류, 분압, 공급

시간, 기판온도, 원료기체 공급 주기의 구성에 따라서 상기 A-B 막의 조성이 조절되는 것일 수 있으며, 및 상기 칼코게나이드화 과정의 C 원료기체의 종류, 분압, 공급시간, 기판온도, C 원료기체 공급과 퍼지단계의 반복 사이클(cycle) 수에 따라 상기 A-B-C 상변화 물질막의 조성이 조절되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0097] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 두께는 서로 동일하거나 상이할 수 있으며, 상기 상변화 각 층의 두께는 특별히 제한되지 않으며, 원하는 상변화 물질막의 제조를 위해 설계자에 의해 자유롭게 변경될 수 있다.

- [0098] 본원의 일 구현예에 있어서, 상기 상변화 물질막 각 층의 두께는 각각 독립적으로 약 0.1 nm 내지 약 50 nm인 것일 수 있으나, 이에 제한되지 않는다. 예를 들어, 상기 상변화 물질막 각 층의 두께는 약 0.1 nm 내지 약 50 nm, 약 1 nm 내지 약 50 nm, 약 10 nm 내지 약 50 nm, 약 20 nm 내지 약 50 nm, 약 30 nm 내지 약 50 nm, 약 40 nm, 약 50 nm, 약 40 nm, 약 0.1 nm 내지 약 40 nm, 약 10 nm 내지 약 40 nm, 약 30 nm, 약 0.1 nm 내지 약 20 nm, 약 1 nm 내지 약 30 nm, 약 10 nm 내지 약 20 nm, 약 0.1 nm 내지 약 10 nm, 약 10 nm 내지 약 20 nm, 약 10 nm 내지 약 20 nm, 약 10 nm 내지 약 10 nm, 또는 약 0.1 nm 내지 약 1 nm인 것일 수 있으나, 이에 제한되지 않는다.

- [0099] 본원의 일 구현예에 있어서, 상기 분리막에 포함되는 상기 비옥사이드계 물질은, 구체적으로, Ti, Ta, W, Hf, Zr, Ru, Mo, Co, Ni, Mn및 이들의 질화물 또는 칼코겐화합물, 탄소계 물질, SiN, SiC, SiCN, AlN, BN (boron nitride), 및 CN (carbon nitride) 로 이루어진 군으로부터 선택되는 것을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 상기 탄소계 물질은, 예를 들어, 탄소, CNT, 그래핀 등을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 상기 칼코겐 화합물은 본 기술 분야에 공지된 것들을 특별히 제한 없이 사용될 수 있으며, 예를 들어, 전이금속 칼코겐 화합물(Transition Metal Dichalcogenide: TMDC)을 사용할 수 있으며, 구체적으로, MoS<sub>2</sub>, WS<sub>2</sub>, MoSe<sub>2</sub>, WSe<sub>2</sub>, MoTe<sub>2</sub> 또는 MoSe<sub>2</sub>의 전이금속 칼코겐 화합물을 사용할 수 있으나, 이에 제한되는 것은 아니다.

- [0100] 상기 분리막의 간격은 적층되는 상변화 물질막의 두께에 따라 결정되며 상기 분리막의 두께는 상변화 특성에 따라 설계자에 의해 자유롭게 변경 할 수 있다.

- [0101] 본원의 일 구현예에 있어서, 상기 분리막은 상기 상변화 물질막의 충들 사이의 원소 이동을 방지하는 것으로서, 비옥사이드계 물질로서 전기 전도성 물질 또는 부도체를 포함하는 것이고, 절연막은 제외되는 것일 수 있다. 이는, 절연막에 포함되는 산소 성분은 메모리 소자에 좋지 않은 영향을 끼칠 수 있기 때문이다. 본원의 일 구현예에 있어서, 상기 분리막 각 충의 두께는 서로 동일하거나 상이할 수 있으며, 상기 분리막 각 충의 두께는 특별히 제한되지 않으며, 원하는 상변화 물질막의 제조를 위해 설계자에 의해 자유롭게 변경될 수 있다.

- [0102] 본원의 일 구현예에 있어서, 상기 분리막 각 층의 두께는 각각 독립적으로 약 0.1 nm 내지 약 10 nm인 것일 수 있으나, 이에 제한되지 않는다. 예를 들어, 상기 분리막 각 층의 두께는 약 0.1 nm 내지 약 10 nm, 약 0.1 nm 내지 약 5 nm, 약 0.1 nm 내지 약 3 nm, 약 0.1 nm 내지 약 1 nm, 약 1 nm 내지 약 10 nm, 약 1 nm 내지 약 5 nm, 또는 약 1 nm 내지 약 3 nm 일 수 있으나, 이에 제한되지 않는다.

- [0103] 본원의 일 구현예에 있어서, 상기 상변화 물질막 각 층의 두께와 상기 분리막 각 층의 두께는 서로 동일하거나 상이할 수 있으며, 상기 두께는 특별히 제한되지 않는다. 예를 들어, 세 층의 상변화 물질막과 두 층의 상기 분리막을 갖는 경우, 상변화 물질막 1 및 상변화 물질막 2 사이의 분리막 두께는 약 2 nm, 상변화 물질막 2 및 상변화 물질막 3 사이의 분리막 두께는 약 5 nm일 수 있으나, 이에 제한되지 않는다.

- [0104] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 상변화 온도는 약 100℃ 내지 약 500℃ 범위인 것일 수 있으나, 이에 제한되지 않을 수 있다. 예를 들어, 상기 상변화 물질막의 각 층의 상변화 온도는 약 100℃ 내지 약 500℃, 약 200℃ 내지 약 500℃, 약 300℃ 내지 약 500℃, 약 400℃ 내지 약 500℃, 약 100℃ 내지 약 300℃, 약 200℃ 내지 약 400℃, 약 300℃, 약 200℃ 내지 약 300℃, 또는 약 100℃ 내지 약 200℃ 범위인 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0105] 본원의 일 구현예에 있어서, 상기 상변화 물질막의 각 층의 상변화 온도는 상기 상변화 물질막의 각 층의 조성 에 따라 조절되는 것일 수 있으나, 이에 제한되지 않을 수 있다.

- [0107] 이하, 본원의 다층 상변화 물질막 및 이를 포함하는 메모리 소자의 구현예들을 도면을 참조하여 설명한다.

- [0108] 도 1을 참조하여 보면, 분리막이 없는 종래의 다층 구조의 상변화 메모리 소자(도 1(a))는 셋(set)/리셋(reset) 동작 시 인가된 전기 펄스에 의해 물질은 결정질/비정질로의 상변화를 일으키며, 이때, 인가 전류에 의해 상변화 물질 원자가 확산하게 되고 각기 다른 조성이었던 상변화 물질막 층들이 하나의 조성으로 점차 섞이게 되어, 도1(b)와 같이, 서로 다른 상변화 물질 1 및 2가 접촉되는 부분에서 새로운 상변화 물질 3이 형성되기 시작한다. 이후, 도 1(c)와 같이 조성이 모두 섞여 하나의 상변화 물질 3이 된다면 멀티-레벨 코딩(multi-level coding)의 장점을 잃게 되고 결과적으로 단일 상변화 물질을 사용한 소자와 같은 특성을 보이거나 또는 셀 수명이 끝나게 된다.

- [0109] 그러나, 본원의 일 구현예에 따라 제조되는 도 2와 같은 상변화 메모리 소자는, 조성이 상이한 다층 상변화 물질층(M1, M2, M3) 사이에 분리막(S1, S2)이 삽입됨으로써 반복적인 셋/리셋에서도 상변화 물질층들의 조성 섞임을 방지할 수 있으며, 이에 따라, 멀티-레벨(multi-level) 특성을 갖는 다층 상변화 물질막(40) 상태를 지속적으로 유지 할 수 있게 된다. 상기 멀테-레벨 특성은 조성이 상이한 상기 다층 상변화 물질막에 의한 것으로서, 상기 조성이 상이한 상기 다층 상변화 물질막을 형성하는 방법은 물리적 기상 증착법, 화학벽 기상 증착법, 또는 원자층 중착법에 의해 수행되는 것이며 이에 제한되지 않는다.

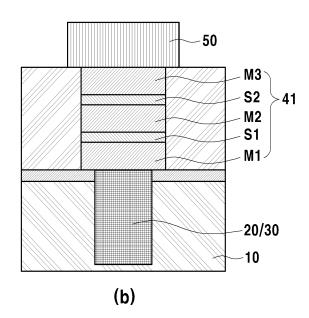

- [0110] 도 3은, 컨파인드 구조에 적용된 본원의 일 구현예에 따른 다층 상변화 물질막으로서, 컨파인드 구조에 각 층의 조성이 상이한 다층 상변화 물질 및 분리막이 형성된 두 가지 구조를 나타낸 것이다. 종래의 원자층 증착법으로 성장시킨 구조막은 도 3(a)이고, 본원의 일 구현예에 따라 기재 상에 형성된 홀(hole) 내에 선택적 성장을 이용하여 증착시킨 다층 상변화 물질막 구조는 도 3(b)와 같다.

- [0111] 상기 도 2 또는 도 3(b)의 구현예는, 3 개의 서로 상이한 상변화 물질층(M1, M2, M3) 및 그들의 사이에 2 개의 분리막(S1,S2)을 포함하는 다층 상변화 물질막을 포함하는 메모리 소자를 나타낸다.

- [0112] 예를 들어, 3 개의 서로 상이한 상변화 물질층(M1, M2, M3)은 하기 식 1 및 식 2와 같은 비정질 상태 저항들 (R<sub>a</sub>)과 결정화 온도들(T<sub>c</sub>)의 특성을 만족할 수 있으나, 이에 제한되지 않는다:

- [0113] (4) 1)  $R_a^{M1} < R_a^{M2} < R_a^{M3}$ ;

- [0114] (4)  $T_c^{M1} > T_c^{M2} > T_c^{M3}$ .

- [0115] 상기 식 2에서 각 결정화 온도들의 T(Tc<sup>M1</sup> Tc<sup>M2</sup> 또는 Tc<sup>M2</sup> Tc<sup>M3</sup>)는 약 10℃ 내지 약 50℃ 정도이다. 예를 들어, 상기 상변화 물질의 각 층의 결정화는 약 100℃, 약 120℃, 및 약 140℃에서 순차적으로 일어나는 것일 수 있으 나, 이에 제한되지 않는다.

- [0116] 상기 식 1 및 식 2를 만족시키는 상변화 물질막은, 예를 들어, 상변화 물질 1(M1)은 GCT(GeCuTe, 예를 들어 Ge<sub>1</sub>Cu<sub>2</sub>Te<sub>3</sub>)이고, 상변화 물질 2(M2)는 SST(SiSbTe, 예를 들어 Si<sub>3.9</sub>Sb<sub>45.6</sub>Te<sub>50.5</sub>)이고, 상변화 물질 3(M3)은 GST(GeSbTe, 예를 들어 Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>)일 수 있으나, 이에 제한되지 않는다.

- [0117] 또는, 상기 상변화 물질막의 제조는, A-B 상변화 물질막을 먼저 증착 후 상기 A-B 상변화 물질막을 칼코게나이 드화함으로써 제조될 수 있으며, 이러한 방법을 이용하여 각 층의 상변화 물질막의 조성을 상이하게 조절할 수 있다.

- [0118] 상기 상변화 물질막 1(M1)과 제 1 전극 사이에 히터가 위치할 수 있고, 상기 히터는 도전막, 예를 들어, Pt 막, W 막, Ti 막, Al 막, TiN 막, TaN 막, 또는 Ni 막일 수 있으나, 이에 제한되지 않을 수 있다. 또한, 상기 분리 막은, 비옥사이드계 물질로서, 구체적으로, Ti, Ta, W, Hf, Zr, Ru, Mo, Co, Ni, Mn 및 이들의 질화물 또는 칼코겐화합물, 탄소계 물질, SiN, SiC, SiCN, AlN, BN (boron nitride), 및 CN (carbon nitride)로 이루어진 군으로부터 선택되는 것을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 상기 탄소계 물질은, 예를 들어, 탄소, CNT, 또는 그래핀 등을 포함하는 것일 수 있으나, 이에 제한되지 않을 수 있다. 상기 칼코겐 화합물은 본 기술 분야에 공지된 것들을 특별히 제한 없이 사용될 수 있으며, 예를 들어, 전이금속 칼코겐 화합물 (Transition Metal Dichalcogenide: TMDC)을 사용할 수 있으며, 구체적으로, MoS<sub>2</sub>, WS<sub>2</sub>, MoSe<sub>2</sub>, WSe<sub>2</sub>, MoTe<sub>2</sub> 또는 MoSe<sub>2</sub>의 전이금속 칼코겐 화합물을 사용할 수 있으나, 이에 제한되는 것은 아니다.

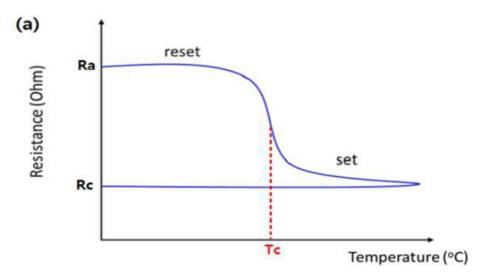

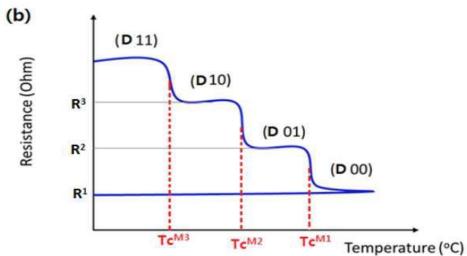

- [0119] 도 4는, (a) 종래의 단일층 상변화 물질막 및 (b) 본원의 일 구현예에 따른 분리막을 포함하는 다층 상변화 물질막의 온도에 따른 저항 변화를 나타내는 그래프로서, 상변화 물질일 경우의 셋/리셋 거동을 대략적으로 나타

낸 것이다. 조성이 상이한 다층의 상변화 물질을 적층한 경우 도 4(b)와 같이 각 층마다 다른 상변화(결정화) 온도를 가지기 때문에 멀티 코딩이 가능하다. 구체적으로, 도 4(b)는 3 가지 상변화 물질층(M1, M2, M3)을 포함하는 메모리 소자의 상변화 온도 및 저항 관계를 나타내고 있으며, 상기 식 1 및 식 2와 같은 비정질 상태 저항들(Ra)과 결정화 온도들(Tc)의 특성을 만족시킨다.

- [0120] 상기 상변화 물질막은 메모리 소자의 전극에 인가되는 전류에 의해 결정화 (Set)되거나 비정질화 (reset)된다. 이때 인가되는 전류의 크기나 지속시간에 따라 상변화 물질의 온도를 조절할 수 있다. 도 4(a)는 기존의 단일 상변화 메모리 소자의 온도에 따른 저항 변화를 도식화 한 것이다. 단일 상변화 물질로 구성되어 있기 때문에 데이터를 1 또는 0, 두가지 상태로만 기록이 가능하다. 본원에 따른 다층 상변화 물질을 적충하여 멀티 레이어 특성을 갖는 메모리 소자의 온도에 따른 저항 변화는 도 4(b) 와 같다. 도 4(b)는 상변화 물질 M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>가 차례로 적층 되어있고, 이들의 상전이 온도 T<sub>c</sub>가 T<sub>c</sub><sup>M2</sup>> T<sub>c</sub><sup>M2</sup>> T<sub>c</sub><sup>M3</sup> 일 때의 저항 변화를 도식화 하였다. 결정화된 상변화 물질 M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>의 저항을 각각 R<sub>c</sub><sup>M3</sup>, R<sub>c</sub><sup>M2</sup>, R<sub>c</sub><sup>M1</sup>로 표현하였다. 상변화 물질 M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>의 상전이 온도가 각자 다른 점을 이용하여 모두 비정질 상태일 때의 데이터를 D<sub>11</sub>, T<sub>c</sub><sup>M3</sup>의 온도 이상에서M<sub>3</sub>의 결정화 되었을 때의 데이터를 D<sub>-10</sub>, T<sub>c</sub><sup>M2</sup>의 온도 이상에서 M<sub>1</sub>의 결정화가 되었을 때의 데이터를 D<sub>00</sub>으로 나타낼 수 있다. 도 4(b)의 세로축의 R<sup>1</sup>, R<sup>2</sup>, 및 R<sup>3</sup>는 상변화 물질층들의 적층에 의한 전체 저항을 나타낸다.

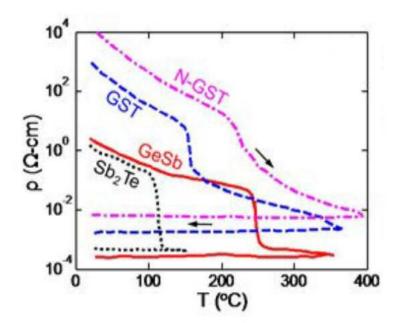

- [0121] 도 5는, 본원의 일 구현예에 따른 분리막을 포함하는 다층 상변화 물질막을 포함하는 메모리 소자 제조 시 사용될 수 있는 다양한 상변화 물질 박막(두께 50 nm)의 온도에 따른 비저항의 변화를 나타내는 참고 그래프 [참고문헌: S. Raoux et al., J. Appl. Phys. 102, 094305 (2007)]로서, 도 5에서 화살표는 승온, 냉각의 방향을 나타낸다. 도면에 나타낸 바와 같이, 비정질상과 결정질상 사이의 저항이 4 오더(order) 이상 변화하는 GST (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>)와 같은 상변화 물질의 저항에 의하여 데이터 (1 또는 0)가 코딩될 수 있고, 이러한 상변화 물질을 이용하여 제조된 메모리 소자에 있어서 메모리 상태는 빠른 전기 펄스 (< 10 ns)를 이용하여 가역적으로 스위칭될 수 있다.

- [0122] 따라서, 본원의 일 구현예에 따른 다층 상변화 물질막은, 다양한 상변화 물질막 사이에 전기 전도도가 높거나 부도체인 비옥사이드계 물질을 포함하는 분리막을 포함함으로써 전압 인가에 따른 반복적인 상변화에도 상기 분리막에 의해 충간 원소 이동이 방지되고, 위층 및 아래층의 조성이 섞이는 것을 방지할 수 있는 효과가 있으며, 이에 따라 멀티 레벨 특성을 유지할 수 있다.

- [0123] 또한, 본원의 일 구현예에 따른 다층 상변화 물질막이 조성이 상이한 다층의 상변화 물질막을 포함하는 경우, 각 층마다 상이한 결정화 온도를 가짐으로써 멀티 코딩(multi coding)이 가능한 특성이 있다.

- [0125] 전술한 본원의 설명은 예시를 위한 것이며, 본원이 속하는 기술분야의 통상의 지식을 가진 자는 본원의 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 쉽게 변형이 가능하다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다. 예를 들어, 단일형으로 설명되어 있는 각 구성 요소는 분산되어 실시될 수도 있으며, 마찬가지로 분산된 것으로 설명되어 있는 구성 요소들도 결합된 형태로 실시될 수도 있다.

- [0126] 본원의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위, 그리고 그 균등 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본원의 범위에 포함되는 것으로 해 석되어야 한다.

## 부호의 설명

[0128] 10: 기재 20:히터 30:제1전극

40,41: 다층 상변화 물질막 50: 제 2 전극

S, S1, S2: 분리막

M1, M2, M3: 상변화 물질 또는 상변화 물질층

# 도면

# 도면1

# 도면2

도면3

도면4

*도면5*

## 【심사관 직권보정사항】

【직권보정 1】

【보정항목】청구범위

【보정세부항목】청구항 제1항 9째줄

【변경전】

상기 제조된 A-B막을

【변경후】

상기 형성된 A-B막을

# 【직권보정 2】

【보정항목】청구범위

【보정세부항목】청구항 제17항 13째줄

【변경전】

상기 제조된 A-B막을

【변경후】

상기 형성된 A-B막을

# 【직권보정 3】

【보정항목】 청구범위

【보정세부항목】청구항 제16항 2째줄

【변경전】

상기 상변화 물질막

【변경후】

상기 다층 상변화 물질막

# 【직권보정 4】

【보정항목】청구범위

【보정세부항목】청구항 제11항 2째줄

【변경전】

상기 상변화 물질막

【변경후】

상기 다층 상변화 물질막